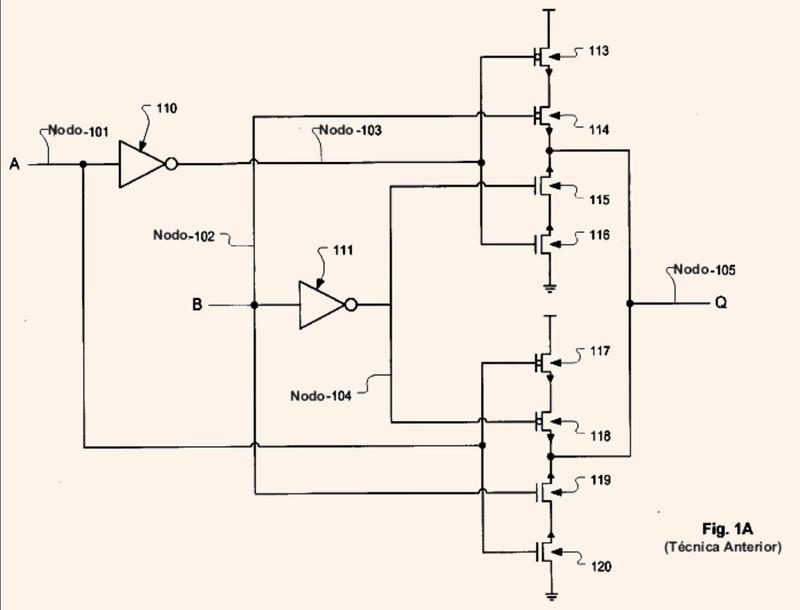

Circuito y diseños para lógica XOR y XNOR.

Un circuito lógico exclusivo OR, que comprende:

un primer inversor (310) de entrada que tiene una entrada conectada a un primer nodo (301) de entrada;

un segundo inversor (311) de entrada que tiene una entrada conectada a un segundo nodo (302) de entrada;

un inversor (317) de salida que tiene una salida conectada a un nodo (307) de salida;

una puerta (350) de transmisión conectada para ser controlada por el estado lógico presente en el primer nodo de entrada, la puerta de transmisión se conecta para pasar a través de una versión del estado lógico presente en el segundo nodo de entrada al nodo de salida cuando se controla para transmitir por el estado lógico presente en el primer nodo de entrada, la puerta de transmisión definida por un segundo transistor (313) NMOS y un primer transistor (314) PMOS, el segundo transistor NMOS tiene una primera terminal de difusión conectada a la salida del segundo inversor de entrada, el segundo transistor NMOS tiene una segunda terminal de difusión conectada a la entrada del inversor de salida, el segundo transistor NMOS que tiene un electrodo de puerta conectado a una salida del primer inversor de entrada, el primer transistor PMOS tiene una primera terminal de difusión conectada a la salida del segundo inversor de entrada, el primer transistor PMOS tiene una segunda terminal de difusión conectada a la entrada del inversor de salida, el primer transistor PMOS que tiene un electrodo de puerta conectado a el primer nodo de entrada; y

el estado lógico (370) alto conectado para ser controlado por el estado lógico presente en el primer nodo de entrada y el estado lógico presente en el segundo nodo de entrada, el estado lógico alto conectado para activar un estado presente en el nodo de salida bajo cuando el estado lógico presente en el primer nodo de entrada y el estado lógico presente en el segundo nodo de entrada son altos, el estado lógico alto definido por un segundo transistor (315) PMOS y un tercer transistor (316) PMOS, el segundo transistor PMOS tiene una primera terminal de difusión conectada a un suministro de potencia, el segundo transistor PMOS tiene una segunda terminal de difusión conectada a una primera terminal de difusión del tercer transistor PMOS, el tercer transistor PMOS tiene una segunda terminal de difusión conectada al inversor de entrada y caracterizado por una puerta (360) de paso conectada para ser controlada por un estado lógico presente en el segundo nodo de entrada, la puerta de paso se conecta para pasar a través de una versión de un estado lógico presente en el primer nodo de entrada al nodo de salida cuando se controla para transmitir por el estado lógico presente en el segundo nodo de entrada, la puerta de paso definida por un primer transistor (312) NMOS que tiene una primera terminal de difusión conectada a una salida del primer inversor de entrada, el primer transistor NMOS tiene una segunda terminal de difusión conectada a una entrada del inversor de salida, el primer transistor NMOS que tiene un electrodo de puerta conectado a una salida del segundo inversor de entrada; y por ya sea el segundo transistor PMOS que tiene un electrodo de puerta conectado a la salida del segundo inversor de entrada con el tercer transistor PMOS que tiene un electrodo de puerta conectado a la salida del primer inversor de entrada o el segundo transistor PMOS que tiene un electrodo de puerta conectado a la salida del primer inversor de entrada con el tercer transistor PMOS que tiene un electrodo de puerta conectado a la salida del segundo inversor de entrada.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/US2010/031650.

Solicitante: Tela Innovations, Inc.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 485 Alberto Way, Suite 115 Los Gatos, CA 95032 ESTADOS UNIDOS DE AMERICA.

Inventor/es: BECKER,SCOTT T.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H03K19/21 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03K TECNICA DE IMPULSO (medida de las características de los impulsos G01R; modulación de oscilaciones sinusoidales por impulsos H03C; transmisión de información digital, H04L; circuitos discriminadores de detección de diferencia de fase entre dos señales de conteo o integración de ciclos de oscilación H03D 3/04; control automático, arranque, sincronización o estabilización de generadores de oscilaciones o de impulsos electrónicos donde el tipo de generador es irrelevante o esta sin especificar H03L; codificación, decodificación o conversión de código, en general H03M). › H03K 19/00 Circuitos lógicos, es decir, teniendo al menos dos entradas que actúan sobre una salida (circuitos para sistemas de computadores que utilizan la lógica difusa G06N 7/02 ); Circuitos de inversión. › Circuitos O EXCLUSIVO, es decir, que dan una señal de salida si existe una sola señal de entrada; Circuitos de COINCIDENCIA, es decir, dan una señal de salida si todas las señales de entrada son idénticas.

PDF original: ES-2565440_T3.pdf

Patentes similares o relacionadas:

Determinación inductiva de la posición, del 30 de Enero de 2019, de ZF FRIEDRICHSHAFEN AG: Dispositivo para la determinación inductiva de la posición que comprende: - una bobina ; - un elemento para influir en un campo magnético […]

Divisor de reloj programable de alta velocidad, del 9 de Enero de 2019, de QUALCOMM INCORPORATED: Un procedimiento para dividir una señal de reloj de entrada por una proporción de división programable, el procedimiento que comprende: contar , en los bordes […]

Diseños para lógica XOR y XNOR, del 8 de Junio de 2016, de Tela Innovations, Inc: Un diseño de circuito exclusivo OR lógico, que comprende: seis transistores PMOS; y cinco transistores NMOS, en el que los cinco transistores […]

MULTIPLICADOR DE FRECUENCIA QUE COMPRENDE UN ARBOL DE PUERTAS LOGICAS O-EXCLUSIVO DE TIPO CMOS., del 16 de Octubre de 1999, de BULL S.A.: LAS PUERTAS DE TIPO O-EXCLUSIVA DE DOS ENTRADAS (A, B) ESTAN DISPUESTAS EN ESTRUCTURA DE ARBOL POR CAPAS SUCESIVAS DESDE UNA CAPA DE ENTRADA QUE RECIBE SEÑALES […]

INVERSOR CONMUTABLE., del 1 de Abril de 1999, de MENDEZ-VIGO BARASONA, JAVIER: INVERSOR CONMUTABLE QUE SE ACTIVA CUANDO LA BASE EMISOR PUEDA COMPUTAR, ES DECIR, CUANDO LA SUMA DE LAS CORRIENTES SON IGUALES A LA CORRIENTE […]

CIRCUITO SEGURO MONOCANAL PARA LA SALIDA DE UN ABONADO DE BUS, del 1 de Marzo de 2009, de PHOENIX CONTACT GMBH & CO. KG: Circuito de salida con un terminal periférico monocanal para un grupo normalizado de salida de bus, cuyo circuito está destinado a conmutar una carga inductiva […]

CIRCUITO SEGURO MONOCANAL PARA LA SALIDA DE UN ABONADO DE BUS, del 1 de Marzo de 2009, de PHOENIX CONTACT GMBH & CO. KG: Circuito de salida con un terminal periférico monocanal para un grupo normalizado de salida de bus, cuyo circuito está destinado a conmutar una carga inductiva […]

DISPOSITIVO PARA COMPARAR DOS VOCABLOS DE N BITS CADA UNO, del 16 de Agosto de 2007, de ATMEL NANTES SA: Dispositivo de comparación de dos palabras N y P de n bits cada una, caracterizado porque comprende, por lo menos, un bloque comparador de nivel 1 que comprende, a su vez: […]

DISPOSITIVO PARA COMPARAR DOS VOCABLOS DE N BITS CADA UNO, del 16 de Agosto de 2007, de ATMEL NANTES SA: Dispositivo de comparación de dos palabras N y P de n bits cada una, caracterizado porque comprende, por lo menos, un bloque comparador de nivel 1 que comprende, a su vez: […]